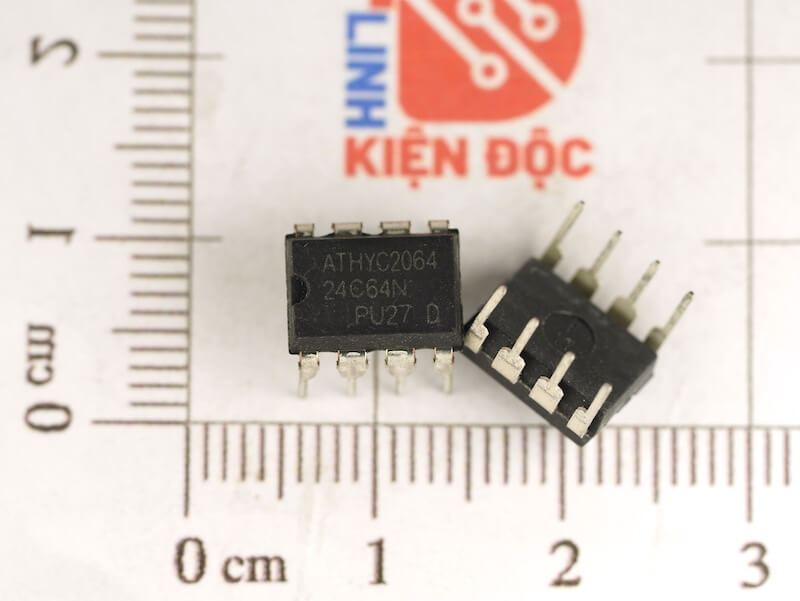

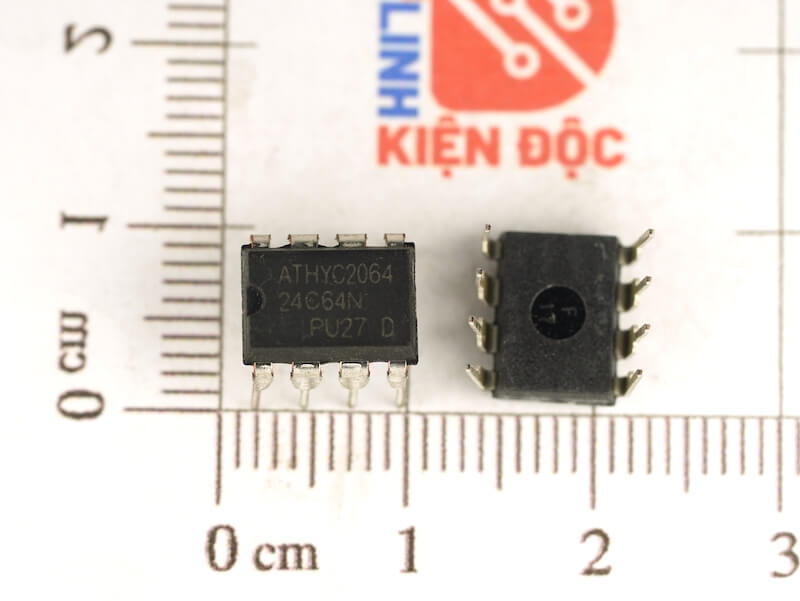

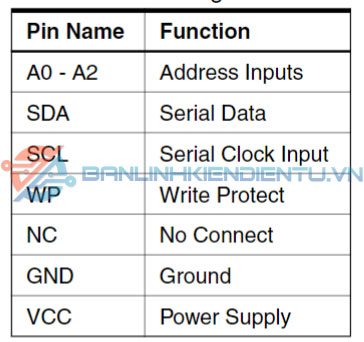

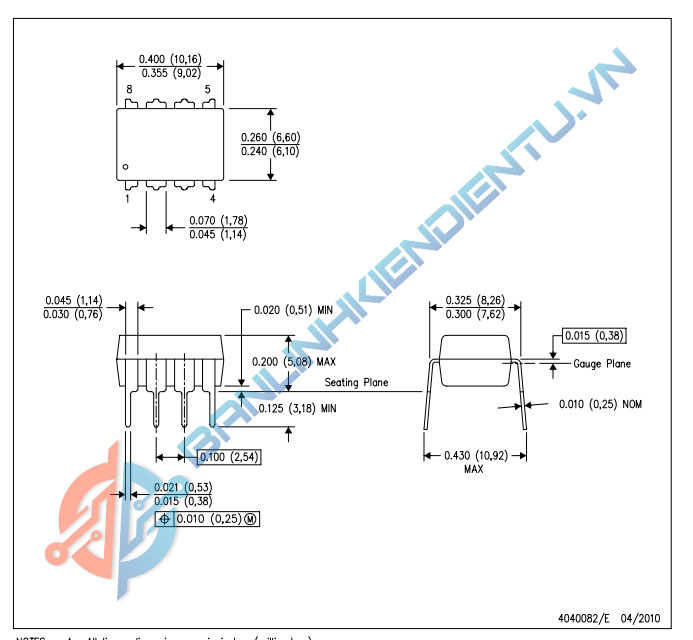

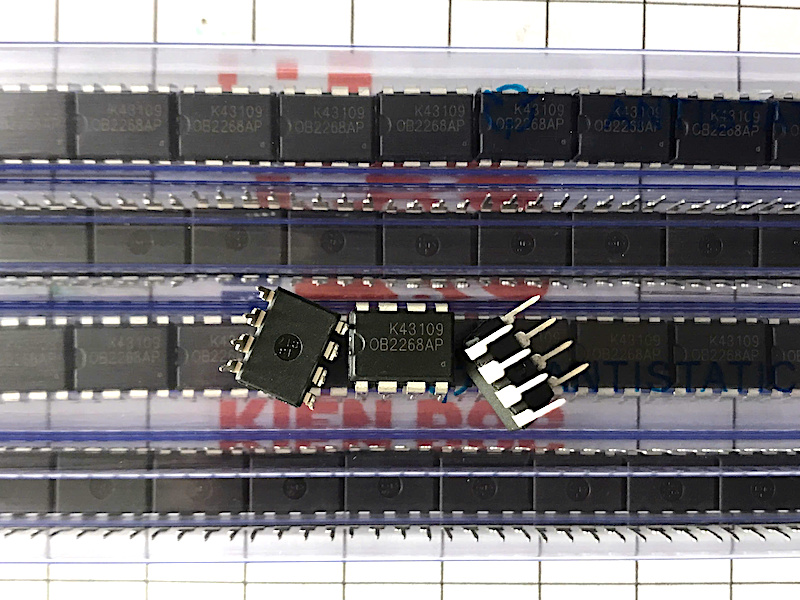

AT24C64N, 24C64N, 24C64 EEPROM DIP8

6,500₫

Mã sản phẩm: 24C64N

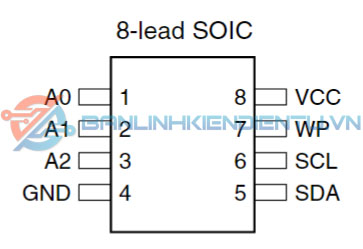

Loại linh kiện: IC

Kiểu chân: DIP8

Hình thức: Mới

Tình trạng: Còn hàng

Vị trí: T5-8

Hỗ trợ trực tuyến

Kinh doanh 1: 0333.595.662

Kinh doanh 2: 0372.770.860

(Giờ làm việc: Buổi sáng: 7:30-12:00, Buổi chiều: 13:30-18:00 từ Thứ 2 đến thứ 7 )

Chú ý: Chỉ gửi đơn hàng tối thiểu 50.000 vnđ và chưa bao gồm phí vận chuyển.

Từ ngày 01/01/2026 giá sản phẩm sẽ tăng lên 8% so với giá đang hiển thị, giá vẫn đang được điều chỉnh, mong quý khách hàng thông cảm và ủng hộ cửa hàng.

Kinh doanh 1: 0333.595.662

Kinh doanh 2: 0372.770.860

(Giờ làm việc: Buổi sáng: 7:30-12:00, Buổi chiều: 13:30-18:00 từ Thứ 2 đến thứ 7 )

Chú ý: Chỉ gửi đơn hàng tối thiểu 50.000 vnđ và chưa bao gồm phí vận chuyển.

Từ ngày 01/01/2026 giá sản phẩm sẽ tăng lên 8% so với giá đang hiển thị, giá vẫn đang được điều chỉnh, mong quý khách hàng thông cảm và ủng hộ cửa hàng.

Đánh giá

Chưa có đánh giá nào.